The microserver concept developed in this project can be used to implement the hard real-time data pipeline of an AO system. It contains a PCIe backplane, which is connected to the FPGA based main board called µXLink. On the PCIe expansion slots of the backplane one or more FPGA based computational boards named µXComp can be inserted and act as accelerator cards to execute the heavy computation required by the new adaptive optics projects. In addition, also other off-the-shelf accelerator cards, e.g. GPUs, can be inserted in the expansion slots of the backplane.

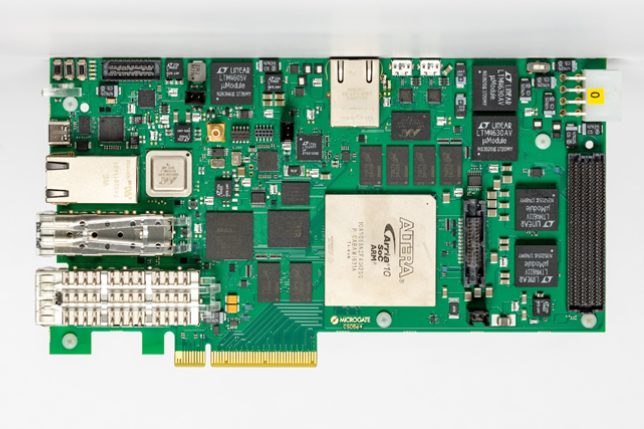

Here is a picture of the first µXlink board after production. Its main component is an Intel FPGA form the ARRIA 10 family that contains a dual-core ARM co-processor on the same die together with the FPGA part building a so-called system-on-chip (SoC). The FPGA part allows to implement a high number of flexible interfaces in order to connect the microserver to different instruments, sensors and deformable mirrors in the various AO projects. The power of the ARM co-processor allows to manage a PCIe root port that controls the communication with the PCIe expansion cards on the backplane. With this ARM co-processor the microserver can work as a stand-alone machine without requiring any Host server or PC.

Here is a picture of the first µXcomp board after production. The development of this board was mainly but not exclusively targeting to provide a highly parallelized implementation of multiply and accumulate operations in floating-point MACs to calculate large Matrix-Vector-Multiplicatons (MVM) in a time-deterministic way with low latency. Thanks to the flexibility that a FPGA offers, virtually any other algorithm can be efficiently programmed in it. For the µXComp a FPGA form the same Intel Family ARRIA 10 as for the µXLink was selected with the difference that this FPGA has no co-processor but twice the amount of high-speed transceiver links. The large number of transceiver channels are used to connect a novel external memory device from Micron named HMC to the FPGA and a high number of high speed flexible interfaces as the PCIe x8 Gen3 endpoint connection. The HMC (Hybrid-Memory-Cube) provides a high memory bandwidth; together with the numerous DSP blocks, this allows achieving high sustained computational throughput; besides that, numerous flexible interfaces are available to connect directly to different data input and output devices.

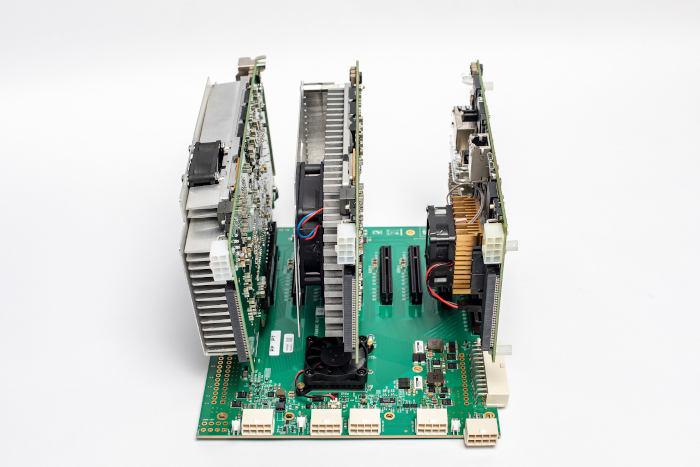

The concept of attaching multiple µXComp boards to one µXLink can be verified with this backplane as a baseline, which is available on the market from One Stop Systems and provides one slot for the host µXLink board and 8 slots for endpoint cards compatible with PCIe up to 8 lanes and up to the Generation 3 data rate standard. The backplane was used to build the first prototype of the Microserver containing one µXLink and two µXComp boards. The communication between these three boards was tested successfully.

The Microserver concept, based on the µXLink and µXComp boards developed in the frame of the project, has been designed and assembled; its operation has been demonstrated, both as functionality of the individual components and as full cluster of boards.

The system provides a valuable solution for the implementation of an energy efficient, compact, rugged standalone microserver, which can accomplish the function of a full RTC system for current-generation AO projects, or be a versatile and flexible interface module with processing capabilities (e.g. pixel per-processing and slopes computing) for the RTCs of the next generation of Extremely Large Telescopes.